|

PCI Express PHY and Controller Solution

This PCI Express (PCIe) solution includes a single-lane endpoint controller (FTPCIE200), a four-lane endpoint controller (FTPCIE210) and transceiver PHYs in various foundry processes.

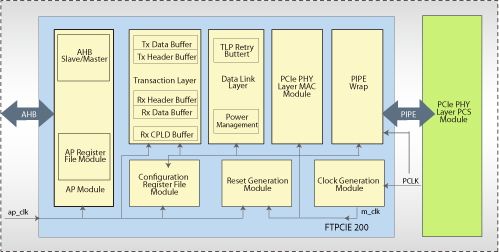

FTPCIE200 is a PCI Express endpoint controller that is compliant with the PCI Express base 2.0 specification and supports single function and single virtual channel. For the transceiver interface, it provides 16-bit PHY interface and is compliant with the PIPE Specification v2.0 (16-bit interface). For the application interface, it provides an AHB bridge.

Functional Block Diagram

Key Features

- Compliant with PCI Express base 2.0 specification

- Supports 16-bit PHY interface and compliant with 16-bit PIPE Specification, v2.0

- Supports AMBA 2.0 AHB interface

- Supports PCI Express Gen2 speed negotiation

- Fully supports PCI Express Transmitter/Receiver transaction ordering rules

- Supports PCI Express native power management ASPM L0s and L1

- Supports single lane with polarity reversal

- Supports single virtual channel and single function

- Supports 6 BARs with 32-bit address space

- Supports INTA interrupt signaling, MSI-X and MSI, including Per-Vector Masking for MSI

- Supports Advanced Error Reporting(AER)

- Supports ECRC generation and checking

PCI Express PHY

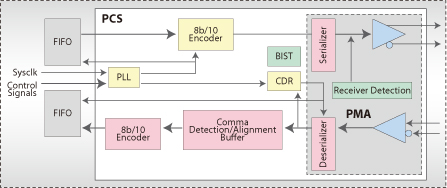

This PCI Express PHY (transceiver) provides a complete range of functions. It is compliant with the PCI Express specifications of version 2.0. This device is capable of transmitting or receiving data of up to 5.0 Gbps.

Functional Block Diagram

Key Features

- Supports the data transfer rate of up to 5.0 Gbps

- Compliant with Intel PIPE macro 2.0

- Supports the PCI Express data receiving recovery function

- Synchronized PCI Express data transmissions

- Integrated Phase-Locked Loop (PLL) oscillator

- Auto-calibrates On-Die Termination resistor Adjustable de-emphasis

- Adjustable TX signal Amplitude

|